Last month, I had the opportunity to attend RISC-V Summit Europe 2025 in Paris, representing Samsung R&D Institute Poland. On Thursday, I presented a poster titled “Enabling RISC-V CI in Open-Source Projects: Challenges and Solutions” – you can find more details about it in the My Poster section below.

Following the summit in Munich last year, it was encouraging to see how the RISC-V ecosystem continues to evolve. From the variety of advanced topics – spanning automotive, HPC, and AI – to the growing emphasis on developer tooling and platform integration, 2025 felt like a year in which the RISC-V ecosystem continued to mature across the stack, even if the software infrastructure is still catching up.

Side note: I’ll be presenting a summary of the RISC-V Summit Europe 2025 as a lightning talk during the FPGA FIRE Workshop in Utrecht on June 27th, 2025. I uploaded a slide deck with more talk highlights.

The summit gathered hundreds of attendees for three packed days of talks, tutorials, demos, and posters in the heart of Paris.

General impressions

Compared to last year’s event, I noticed a stronger emphasis on tooling maturity and cross-domain deployment. While the AI/ML and custom accelerator wave continues, there was a marked increase in presentations that focused on practical engineering work: reproducibility, CI/CD integration, and developer tooling.

In addition, several talks explored the intersection of RISC-V and critical domains such as space, automotive, and security – showing growing confidence in deploying RISC-V beyond labs and into real-world applications.

My poster

This year, I presented my work on “Enabling RISC-V CI in Open-Source Projects: Challenges and Solutions,” which I’ve been working on for quite some time at Samsung. The motivation behind the project was simple: while RISC-V adoption is growing, most upstream open-source projects (in our case, those hosted on Freedesktop.org) still lack automated CI testing for RISC-V. This makes it harder to validate architecture-specific contributions, especially for performance-critical SIMD and RVV (RISC-V Vectors) code.

At Samsung R&D Institute Poland, we tackled this by designing a QEMU-based GitLab CI template framework that allows testing across multiple architectures – RISC-V included – without needing dedicated hardware.

The approach uses Docker-based runners, native toolchains (both GNU and LLVM), and multi-architecture images to support RVV and other SIMD backends across platforms.

We first rolled this out for Pixman, a pixel manipulation library used by Cairo and some Wayland compositors, where we added RVV SIMD support and uncovered several bugs through automated CI. From there, we are in the process of applying the same model to GStreamer Orc, which dynamically compiles vectorized media pipelines, and in the future to Opus, a widely-used audio codec.

The CI templates are modular and reusable, allowing projects to run native tests on supported architectures using Docker and QEMU – all integrated into GitLab’s pipelines. The pipeline generates a unified coverage report for all platforms using the gcovr tool, which greatly improves test visibility and bug triaging.

For RVV in particular, testing across multiple VLENs exposed subtle configuration-specific issues that would have gone unnoticed in manual testing, especially with the limited amount of hardware available on the market.

This work shows how relatively small infrastructure changes can have a large impact on open-source contribution velocity and software robustness for emerging architectures like RISC-V.

If you’d like to dive into the technical details or reuse our approach, everything is publicly available on GitHub, and the template itself is hosted (for now) on FDO’s GitLab.

Hardware

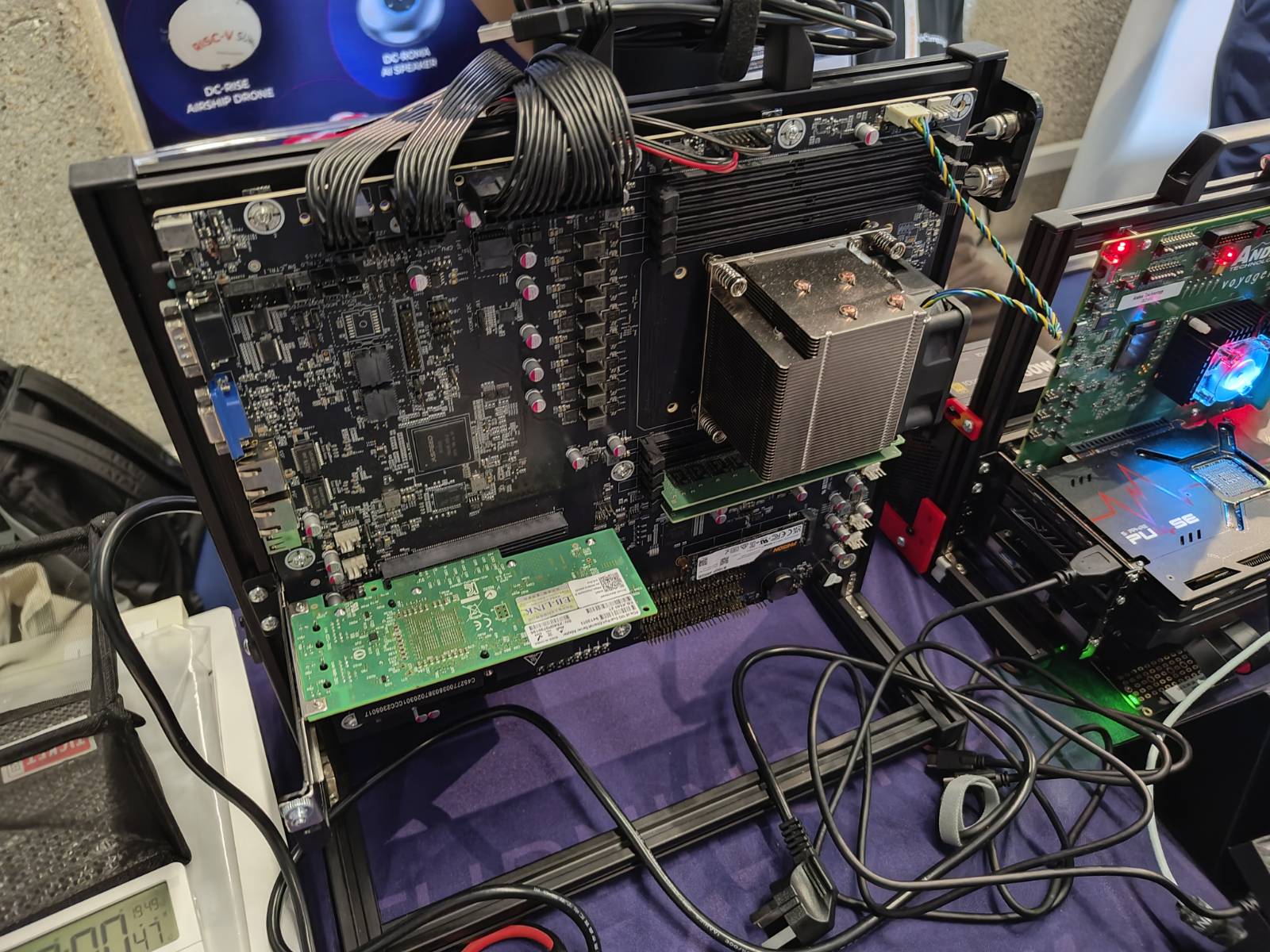

This year’s expo floor featured a wide range of RISC-V hardware – from compact microcontrollers and SoCs to full development boards and AI-capable edge devices. The DeepComputing booth showcased their latest DC-ROMA RISC-V AI PC and a motherboard for the Framework Laptop. It’s clear that the hardware ecosystem is becoming more diverse and deployment-ready. Below, I’ve included a few photos of the hardware, courtesy of my colleague from Samsung, Filip Wasil.

Presentation highlights

As always, the conference featured an excellent lineup of speakers representing academia, industry, and open-source communities. While it’s impossible to cover everything, here are some of the talks and sessions that stood out to me – either for their technical depth, unique perspective, or practical relevance to RISC-V adoption.

RISC-V State of the Union

A keynote-level update from one of RISC-V’s founders. Krste Asanović, Chief Architect at SiFive, reflected on how far the ecosystem has come since the ISA’s inception (this year marks the 15th birthday of RISC-V!) and laid out a forward-looking strategy for growth. He touched on RISC-V profiles, DSP extension improvements, documentation cleanup, and early work on long instructions.

The RISE Project: Advancing RISC-V Software

This joint talk by Nathan Egge (Google) and Ludovic Henry (Rivos) is especially close to my heart, as I’m part of the RISE project within Samsung. The presentation offered updates on RISC-V software enablement, the open-source contribution awards program, and new training materials (with optional certification). A great summary of the software community’s progress.

The Significance of the RVA23 Profile in Advancing RISC-V Ecosystem

Mark Hayter (Rivos) discussed the current state of RISC-V profiles and their roadmap. He introduced RVM23 for embedded systems and hinted at RVA30 as the next major milestone. Until then, RVA23 will get minor updates with optional ISA extensions. This talk is a great primer if you’re still unfamiliar with how profiles simplify platform compatibility and software development.

RISC-V: Powering the Future of High Performance Computing?

Nick Brown, chair of the HPC SIG at RISC-V International, spoke on the importance of open standards in HPC. He mentioned the free-access RISC-V HPC lab, discussed hardware readiness and challenges for RISC-V adoption.

RISC-V: Reaching New Orbits in Space Computing

Lucana Santos from the European Space Agency (ESA) gave a compelling talk on ESA’s shift from SPARC to RISC-V SoCs. She discussed their goals for the next generation of space-grade chips – improved performance, AI/ML support, DSP capabilities, and enhanced fault tolerance. In her view, RISC-V hasn’t just started taking over in space – it already has.

Flex-RV: World’s First Non-silicon RISC-V Microprocessor

This talk introduced Flex-RV, the world’s first RISC-V processor built using a non-silicon, (literally) flexible semiconductor process. It’s really cool to see RISC-V being used on the forefront of new semicon technologies.

Closing thoughts

It’s been great to reconnect with familiar faces from past years and see new contributors join the RISC-V community. Each year, the Summit feels more professional, more collaborative, and more diverse in terms of domains and applications.

I’m already looking forward to the next edition in Bologna – and in the meantime, I’ll be continuing this CI enablement work and hopefully expanding it to even more projects and use cases.